### **General Description**

MAX1846/MAX1847 high-efficiency PWM inverting controllers allow designers to implement compact, lownoise, negative-output DC-DC converters for telecom and networking applications. Both devices operate from +3V to +16.5V input and generate -2V to -200V output. To minimize switching noise, both devices feature a current-mode, constant-frequency PWM control scheme. The operating frequency can be set from 100kHz to 500kHz through a resistor.

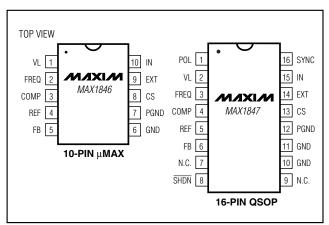

The MAX1846 is available in an ultra-compact 10-pin µMAX package. Operation at high frequency, compatibility with ceramic capacitors, and inverting topology without transformers allow for a compact design. Compatibility with electrolytic capacitors and flexibility to operate down to 100kHz allow users to minimize the cost of external components. The high-current output drivers are designed to drive a P-channel MOSFET and allow the converter to deliver up to 30W.

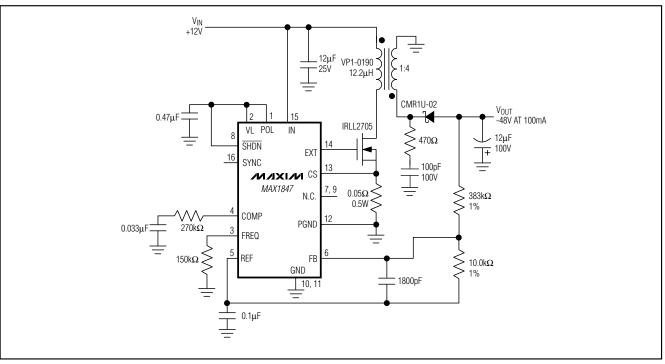

The MAX1847 features clock synchronization and shutdown functions. The MAX1847 can also be configured to operate as an inverting flyback controller with an Nchannel MOSFET and a transformer to deliver up to 70W. The MAX1847 is available in a 16-pin QSOP package.

Current-mode control simplifies compensation and provides good transient response. Accurate current-mode control and over current protection are achieved through low-side current sensing.

### **Applications**

Cellular Base Stations Networking Equipment Optical Networking Equipment **SLIC Supplies** CO DSL Line Driver Supplies Industrial Power Supplies Automotive Electronic Power Supplies Servers

Pin Configurations appear at end of data sheet.

#### Features

- ♦ 90% Efficiency

- ♦ +3.0V to +16.5V Input Range

- ♦ -2V to -200V Output

- ◆ Drives High-Side P-Channel MOSFET

- ♦ 100kHz to 500kHz Switching Frequency

- **♦ Current-Mode, PWM Control**

- ♦ Internal Soft-Start

- **♦ Electrolytic or Ceramic Output Capacitor**

- ♦ The MAX1847 also offers:

Synchronization to External Clock Shutdown **N-Channel Inverting Flyback Option**

### **Ordering Information**

| PART       | TEMP. RANGE    | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX1846EUB | -40°C to +85°C | 10 μMAX     |

| MAX1847EEE | -40°C to +85°C | 16 QSOP     |

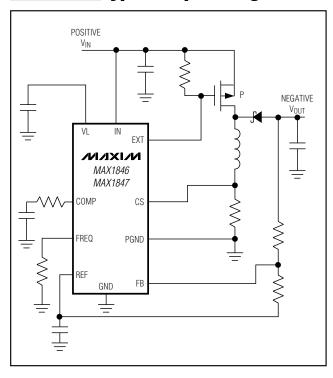

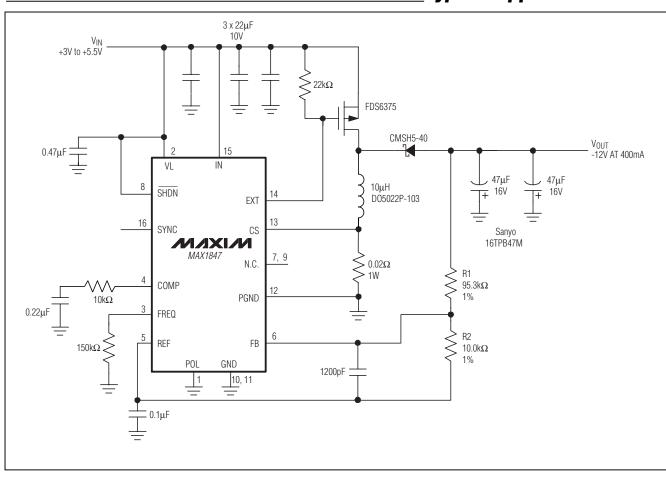

### **Typical Operating Circuit**

#### **ABSOLUTE MAXIMUM RATINGS**

| IN, SHDN to GND                       | 0.3V to +20V              |

|---------------------------------------|---------------------------|

| PGND to GND                           |                           |

| VL to PGND for $V_{IN} \le 5.7V$      | 0.3V to $(V_{IN} + 0.3V)$ |

| VL to PGND for V <sub>IN</sub> > 5.7V | 0.3V to +6V               |

| EXT to PGND                           | 0.3V to $(V_{IN} + 0.3V)$ |

| REF, COMP to GND                      | 0.3V to $(VL + 0.3V)$     |

| CS, FB, FREQ, POL, SYNC to GND.       | 0.3V to +6V               |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |       |

|-------------------------------------------------------|-------|

| 10-Pin μMAX (derate 5.6mW/°C above +70°C)44           |       |

| 16-Pin QSOP (derate 8.3mW/°C above +70°C)69           | 6mW   |

| Operating Temperature Range40°C to +                  | -85°C |

| Junction Temperature+1                                | 50°C  |

| Storage Temperature Range65°C to +1                   |       |

| Lead Temperature (soldering, 10s)+3                   | 800°C |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V\overline{SHDN} = V_{IN} = +12V, SYNC = GND, PGND = GND, RFREQ = 147k\Omega \pm 1\%, C_{VL} = 0.47\mu F, C_{REF} = 0.1\mu F, T_A = 0^{\circ}C$  to +85°C, unless otherwise noted.)

| PARAMETER CONDITIONS          |                                                                                                    | MIN   | TYP  | MAX   | UNITS |

|-------------------------------|----------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| PWM CONTROLLER                | ·                                                                                                  |       |      |       |       |

| Operating Input Voltage Range |                                                                                                    | 3.0   |      | 16.5  | V     |

| UVLO Threshold                | V <sub>IN</sub> rising                                                                             |       | 2.8  | 2.95  | V     |

|                               | V <sub>IN</sub> falling                                                                            | 2.6   | 2.74 |       | v     |

| UVLO Hysteresis               |                                                                                                    |       | 60   |       | mV    |

| FB Threshold                  | No load                                                                                            | -12   | 0    | 12    | mV    |

| FB Input Current              | V <sub>FB</sub> = -0.1V                                                                            | -50   | -6   | 50    | nA    |

| Load Regulation               | C <sub>COMP</sub> = 0.068µF, V <sub>OUT</sub> = -48V,<br>I <sub>OUT</sub> = 20mA to 200mA (Note 1) |       |      | 0     | %     |

| Line Regulation               | $C_{COMP} = 0.068\mu F$ , $V_{OUT} = -48V$ , $V_{IN} = +8V$ to $+16.5V$ , $I_{OUT} = 100mA$        |       | 0.04 |       | %     |

| Current-Limit Threshold       |                                                                                                    | 85    | 100  | 115   | mV    |

| CS Input Current              | CS = GND                                                                                           |       | 10   | 20    | μΑ    |

| Supply Current                | $V_{FB} = -0.1V$ , $V_{IN} = +3.0V$ to $+16.5V$                                                    |       | 0.75 | 1.2   | mA    |

| Shutdown Supply Current       | Shutdown Supply Current SHDN = GND, V <sub>IN</sub> = +3.0V to +16.5V                              |       | 10   | 25    | μΑ    |

| REFERENCE AND VL REGULAT      | FOR                                                                                                |       |      |       |       |

| REF Output Voltage            | I <sub>REF</sub> = 50µA                                                                            | 1.236 | 1.25 | 1.264 | V     |

| REF Load Regulation           | $I_{REF} = 0 \text{ to } 500\mu\text{A}$ -2                                                        |       | -15  | mV    |       |

| VL Output Voltage             | l <sub>VL</sub> = 100μA 3.85 4.25 4.65                                                             |       | 4.65 | V     |       |

| VL Load Regulation            | $I_{VL} = 0.1 \text{mA to } 2.0 \text{mA}$ -20 -60                                                 |       | -60  | mV    |       |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{\overline{SHDN}} = V_{IN} = +12V, SYNC = GND, PGND = GND, R_{FREQ} = 147k\Omega \pm 1\%, C_{VL} = 0.47\mu F, C_{REF} = 0.1\mu F, T_A = 0^{\circ}C$  to +85°C, unless otherwise noted.)

| OSCILLATOR                                  |                                                                  |     |      |      |        |

|---------------------------------------------|------------------------------------------------------------------|-----|------|------|--------|

|                                             | $R_{FREQ} = 500 k\Omega \pm 1\%$                                 | 90  | 100  | 110  |        |

| Oscillator Frequency                        | $R_{FREQ} = 147 k\Omega \pm 1\%$                                 | 255 | 300  | 345  | kHz    |

|                                             | $R_{FREQ} = 76.8 k\Omega \pm 1\%$                                |     | 500  |      |        |

|                                             | $R_{FREQ} = 500k\Omega \pm 1\%$                                  | 93  | 96   | 97   |        |

| Maximum Duty Cycle                          | $R_{FREQ} = 147 k\Omega \pm 1\%$                                 | 85  | 88   | 90   | %      |

|                                             | R <sub>FREQ</sub> = 76.8kz ±1%                                   |     | 80   |      |        |

| SYNC Input Signal Duty-Cycle Range          |                                                                  | 7   |      | 93   | %      |

| Minimum SYNC Input Logic Low<br>Pulse Width |                                                                  |     | 50   | 200  | ns     |

| SYNC Input Rise/Fall Time                   | (Note 2)                                                         |     |      | 200  | ns     |

| SYNC Input Frequency Range                  |                                                                  | 100 |      | 550  | kHz    |

| DIGITAL INPUTS                              |                                                                  |     |      |      |        |

| POL, SYNC, SHDN Input High<br>Voltage       |                                                                  | 2.0 |      |      | ٧      |

| POL, SYNC, SHDN Input Low<br>Voltage        |                                                                  |     |      | 0.45 | V      |

| POL, SYNC Input Current                     | POL, SYNC = GND or VL                                            |     | 20   | 40   | μΑ     |

| CUDN lagget Coursest                        | VSHDN = +5V or GND                                               | -12 | -4   | 0    |        |

| SHDN Input Current                          | V <sub>SHDN</sub> = +16.5V                                       |     | 1.5  | 6    | μΑ     |

| SOFT-START                                  |                                                                  |     |      |      |        |

| Soft-Start Clock Cycles                     |                                                                  |     | 1024 |      | Cycles |

| Soft-Start Levels                           |                                                                  |     | 64   |      |        |

| EXT OUTPUT                                  |                                                                  |     |      |      |        |

| EXT Sink/Source Current                     | $V_{IN}$ = +5V, $V_{EXT}$ forced to +2.5V                        |     | 1    |      | А      |

| EXT On-Resistance                           | EXT high or low, tested with 100mA load, V <sub>IN</sub> = +5V 2 |     | 5    | Ω    |        |

| LAT OF RESISTANCE                           | EXT high or low, tested with 100mA load, V <sub>IN</sub> = +3V   |     | 5    | 10   | 32     |

**Note 1:** Production test correlates to operating conditions.

Note 2: Guaranteed by design and characterization.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{\overline{SHDN}} = V_{IN} = +12V, SYNC = GND, PGND = GND, R_{FREQ} = 147k\Omega \pm 1\%, C_{VL} = 0.47\mu F, C_{REF} = 0.1\mu F, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted.) (Note 3)

| PARAMETER                                           | CONDITIONS                                                                                         | MIN   | MAX   | UNITS |  |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------|-------|-------|-------|--|

| PWM CONTROLLER                                      | 1                                                                                                  | 1     |       |       |  |

| Operating Input Voltage Range                       |                                                                                                    | 3.0   | 16.5  | V     |  |

| 1 N / 1 O The reads also                            | V <sub>IN</sub> rising                                                                             |       | 2.95  | V     |  |

| UVLO Threshold                                      | V <sub>IN</sub> falling                                                                            | 2.6   |       | V     |  |

| FB Threshold                                        | No load                                                                                            | -20   | 20    | mV    |  |

| FB Input Current                                    | V <sub>FB</sub> = -0.1V                                                                            | -50   | 50    | nA    |  |

| Load Regulation                                     | C <sub>COMP</sub> = 0.068µF, V <sub>OUT</sub> = -48V,<br>I <sub>OUT</sub> = 20mA to 200mA (Note 1) | -2    | 0     | %     |  |

| Current Limit Threshold                             |                                                                                                    | 85    | 115   | mV    |  |

| CS Input Current                                    | CS = GND                                                                                           |       | 20    | μΑ    |  |

| Supply Current                                      | $V_{FB} = -0.1V$ , $V_{IN} = +3.0V$ to $+16.5V$                                                    |       | 1.2   | mA    |  |

| Shutdown Supply Current                             | $\overline{SHDN} = GND, \ V_{IN} = +3.0V \text{ to } +16.5V$                                       |       | 25    | μΑ    |  |

| REFERENCE AND VL REGULAT                            | OR                                                                                                 | ·     |       |       |  |

| REF Output Voltage                                  | I <sub>REF</sub> = 50µA                                                                            | 1.225 | 1.275 | V     |  |

| REF Load Regulation                                 | I <sub>REF</sub> = 0 to 500µA                                                                      |       | -15   | mV    |  |

| VL Output Voltage                                   | I <sub>VL</sub> = 100μA                                                                            | 3.85  | 4.65  | V     |  |

| VL Load Regulation I <sub>VL</sub> = 0.1mA to 2.0mA |                                                                                                    |       | -60   | mV    |  |

| OSCILLATOR                                          |                                                                                                    |       |       |       |  |

| Consillator Francisco                               | $R_{FREQ} = 500 k\Omega \pm 1\%$                                                                   | 84    | 116   | T     |  |

| Oscillator Frequency                                | $R_{FREQ} = 147 k\Omega \pm 1\%$                                                                   | 255   | 345   | kHz   |  |

| Maximum Duty Cycle                                  | $R_{FREQ} = 500 k\Omega \pm 1\%$                                                                   | 93    | 98    | %     |  |

| Maximum Duty Cycle                                  | $R_{FREQ} = 147 k\Omega \pm 1\%$                                                                   | 84    | 93    | %     |  |

| SYNC Input Signal Duty-Cycle<br>Range               |                                                                                                    | 7     | 93    | %     |  |

| Minimum SYNC Input Logic Low Pulse Width            |                                                                                                    |       | 200   | ns    |  |

| SYNC Input Rise/Fall Time                           | SYNC Input Rise/Fall Time (Note 2)                                                                 |       | 200   | ns    |  |

| SYNC Input Frequency Range                          |                                                                                                    | 100   | 550   | kHz   |  |

| DIGITAL INPUTS                                      |                                                                                                    |       |       |       |  |

| POL, SYNC, SHDN Input High<br>Voltage               | · · ·                                                                                              |       |       | V     |  |

| POL, SYNC, SHDN Input Low<br>Voltage                |                                                                                                    |       | 0.45  | V     |  |

5

## High-Efficiency, Current-Mode, **Inverting PWM Controller**

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{\overline{S}H\overline{D}N} = V_{IN} = +12V, SYNC = GND, PGND = GND, R_{FREQ} = 147k\Omega \pm 1\%, C_{VL} = 0.47\mu F, C_{REF} = 0.1\mu F, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted.) (Note 3)

| PARAMETER               | CONDITIONS                                           | MIN | MAX | UNITS |  |

|-------------------------|------------------------------------------------------|-----|-----|-------|--|

| POL, SYNC Input Current | POL, SYNC = GND or VL                                |     | 40  | μΑ    |  |

| CUDN Input Current      | $V_{\overline{SHDN}} = +5V \text{ or GND}$           | -12 | 0   |       |  |

| SHDN Input Current      | V <del>SHDN</del> = +16.5V                           |     | 6   | μA    |  |

| EXT OUTPUT              |                                                      |     |     |       |  |

| EXT On-Resistance       | EXT high or low, $I_{EXT} = 100$ mA, $V_{IN} = +5$ V |     | 7.5 | Ω     |  |

| EXT OII-nesisidile      | EXT high or low, $I_{EXT} = 100$ mA, $V_{IN} = +3V$  |     | 12  | 22    |  |

Note 3: Parameters to -40°C are guaranteed by design and characterization.

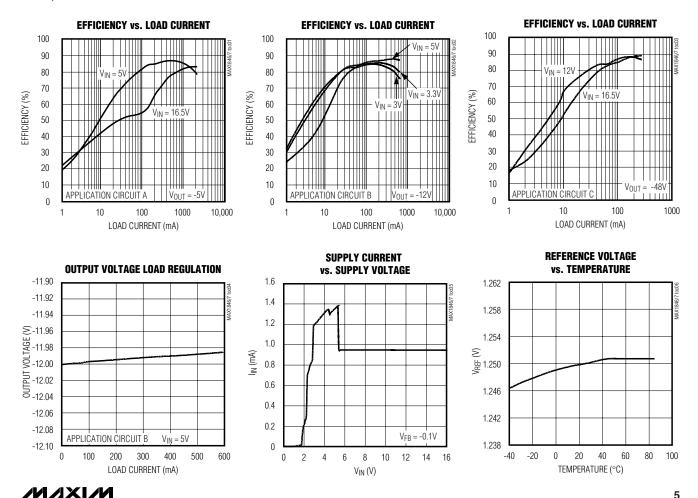

## **Typical Operating Characteristics**

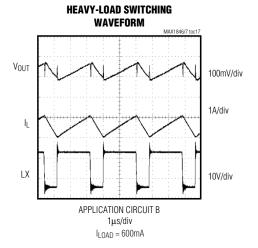

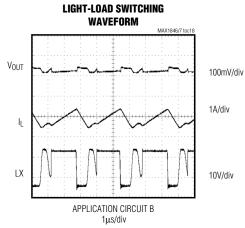

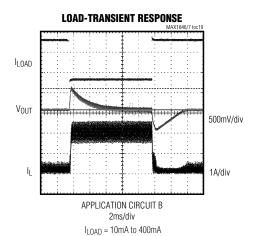

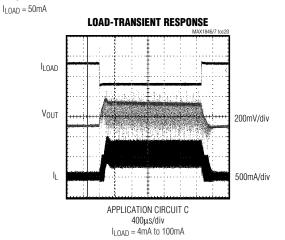

(Circuit references are from Table 1 in the Main Application Circuits section, C<sub>VL</sub> = 0.47µF, C<sub>REF</sub> = 0.1µF, T<sub>A</sub> = +25°C, unless otherwise noted.)

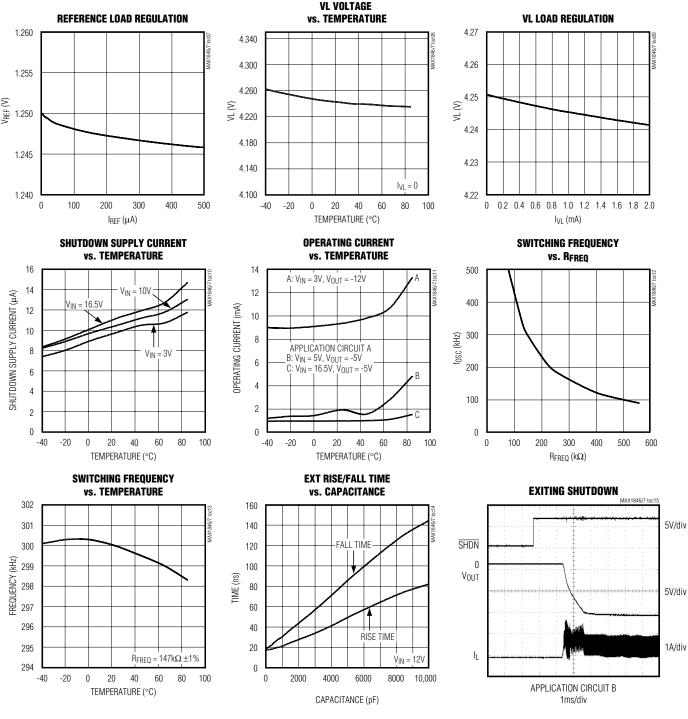

### Typical Operating Characteristics (continued)

(Circuit references are from Table 1 in the *Main Application Circuits* section,  $C_{VL} = 0.47 \mu F$ ,  $C_{REF} = 0.1 \mu F$ ,  $T_A = +25 ^{\circ}C$ , unless otherwise noted.)

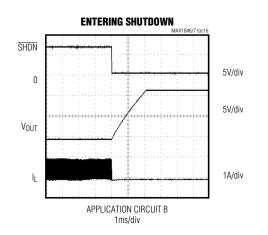

### Typical Operating Characteristics (continued)

(Circuit references are from Table 1 in the *Main Application Circuits* section,  $C_{VL} = 0.47 \mu F$ ,  $C_{REF} = 0.1 \mu F$ ,  $T_A = +25 ^{\circ}C$ , unless otherwise noted.)

## **Pin Description**

| PIN     |         |      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|---------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MAX1846 | MAX1847 | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| _       | 1       | POL  | Sets polarity of the EXT pin. Connect POL to GND to set EXT for use with an external PMOS high-side FET. Connect POL to VL to set EXT for use with an external NMOS low-side FET in transformer-based applications.                                                                                                                                                                                                                            |  |  |

| 1       | 2       | VL   | VL Low-Dropout Regulator. Connect 0.47µF ceramic capacitor from VL to GND.                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 2       | 3       | FREQ | Oscillator Frequency Set Input. Connect a resistor (RFREQ) from FREQ to GND to set the internal oscillator frequency from 100kHz (RFREQ = $500k\Omega$ ) to $500kHz$ (RFREQ = $76.8k\Omega$ ). RFREQ is still required if an external clock is used at SYNC. See Setting the Operating Frequency section.                                                                                                                                      |  |  |

| 3       | 4       | COMP | Compensation Node for Error Amp/Integrator. Connect a series resistor/capacitor network from COMP to GND for loop compensation. See <i>Design Procedure</i> .                                                                                                                                                                                                                                                                                  |  |  |

| 4       | 5       | REF  | 1.25V Reference Output. REF can source up to 500µA. Bypass with a 0.1µF ceramic capacitor from REF to GND.                                                                                                                                                                                                                                                                                                                                     |  |  |

| 5       | 6       | FB   | Feedback Input. Connect FB to the center of a resistor-divider connected between the output and REF. The FB threshold is 0.                                                                                                                                                                                                                                                                                                                    |  |  |

| _       | 7,9     | N.C. | No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| _       | 8       | SHDN | Shutdown Control. Drive SHDN low to turn off the DC-DC controller. Drive high or connect to IN for normal operation.                                                                                                                                                                                                                                                                                                                           |  |  |

| 6       | 10,11   | GND  | Analog Ground. Connect to PGND.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 7       | 12      | PGND | Negative Rail for EXT Driver and Negative Current-Sense Input. Connect to GND.                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 8       | 13      | CS   | Positive Current-Sense Input. Connect a current-sense resistor (R <sub>CS</sub> ) between CS and                                                                                                                                                                                                                                                                                                                                               |  |  |

| 9       | 14      | EXT  | External MOSFET Gate-Driver Output. EXT swings from IN to PGND.                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 10      | 15      | IN   | Power-Supply Input                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| _       | 16      | SYNC | Operating Frequency Synchronization Control. Drive SYNC low or connect to GND to set the internal oscillator frequency with R <sub>FREQ</sub> . Drive SYNC with a logic-level clock input signal to externally set the converter's operating frequency. DC-DC conversion cycles initiate on the rising edge of the input clock signal. Note that when driving SYNC with an external signal, R <sub>FREQ</sub> must still be connected to FREQ. |  |  |

## Typical Application Circuit

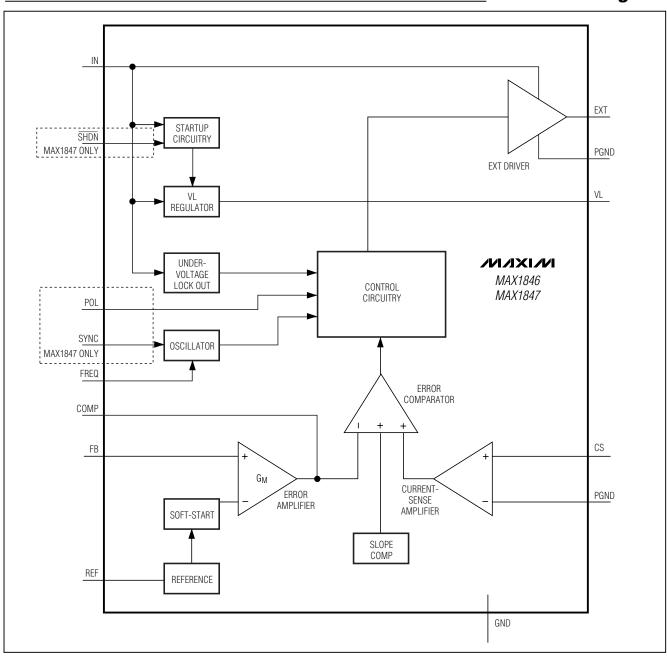

### Functional Diagram

#### **Detailed Description**

The MAX1846/MAX1847 current-mode PWM controller use an inverting topology that is ideal for generating output voltages from -2V to -200V. Features include shutdown, adjustable internal operating frequency or synchronization to an external clock, soft-start, adjustable current limit, and a wide (+3V to +16.5V) input range.

#### **PWM Controller**

The architecture of the MAX1846/MAX1847 current-mode PWM controller is a Bi-CMOS multi-input system that simultaneously processes the output-error signal, the current-sense signal, and a slope-compensation ramp (*Functional Diagram*). Slope compensation prevents subharmonic oscillation, a potential result in current-mode regulators operating at greater than 50% duty cycle. The controller uses fixed-frequency, current-mode operation where the duty ratio is set by the input-to-output voltage ratio. The current-mode feedback loop regulates peak inductor current as a function of the output error signal.

#### Internal Regulator

The MAX1846/MAX1847 incorporate an internal low-dropout regulator (LDO). This LDO has a 4.25V output and powers all MAX1846/MAX1847 functions (excluding EXT) for the primary purpose of stabilizing the performance of the IC over a wide input voltage range (+3V to +16.5V). The input to this regulator is connected to IN, and the dropout voltage is typically 100mV, so that when V<sub>IN</sub> is less than 4.35V, VL is typically V<sub>IN</sub> minus 100mV. When the LDO is in dropout, the MAX1846/MAX1847 still operate with V<sub>IN</sub> as low as 3V. For best performance, it is recommended to connect VL to IN when the input supply is less than 4.5V.

#### Undervoltage Lockout

The MAX1846/MAX1847 have an undervoltage lockout circuit that monitors the voltage at VL. If VL falls below the UVLO threshold (2.8V typ), the control logic turns the P-channel FET off (EXT high impedance). The rest of the IC circuitry is still powered and operating. When VL increases to 60mV above the UVLO threshold, the IC resumes operation from a start up condition (soft-start).

#### Soft-Start

The MAX1846/MAX1847 feature a "digital" soft-start that is preset and requires no external capacitor. Upon startup, the FB threshold decrements from the reference voltage to 0 in 64 steps over 1024 cycles of fosc or fsync. See the *Typical Operating Characteristics* for a scope picture of the soft-start operation. Soft-start is implemented: 1) when power is first applied to the IC,

2) when exiting shutdown with power already applied, and 3) when exiting undervoltage lockout.

#### Shutdown (MAX1847 only)

The MAX1847 shuts down to reduce the supply current to  $10\mu\text{A}$  when  $\overline{\text{SHDN}}$  is low. In this mode, the internal reference, error amplifier, comparators, and biasing circuitry turn off. The EXT output becomes high impedance and the external pullup resistor connected to EXT pulls VEXT to VIN, turning off the P-channel MOSFET. When in shutdown mode, the converter's output goes to 0.

## Frequency Synchronization (MAX1847 only)

The MAX1847 is capable of synchronizing its switching frequency with an external clock source. Drive SYNC with a logic-level clock input signal to synchronize the MAX1847. A switching cycle starts on the rising edge of the signal applied to SYNC. Note that the frequency of the signal applied to SYNC must be higher than the default frequency set by RFREQ. This is required so that the internal clock does not start a switching cycle prematurely. If SYNC is inactive for an entire clock cycle of the internal oscillator, the internal oscillator takes over the switching operation. Choose RFREQ such that fosc =  $0.9 \times fSYNC$ .

#### EXT Polarity (MAX1847 only)

The MAX1847 features an option to utilize an N-channel MOSFET configuration, rather than the typical P-channel MOSFET configuration (Figure 1). In order to drive the different polarities of these MOSFETs, the MAX1847 is capable of reversing the phase of EXT by 180 degrees. When driving a P-channel MOSFET, connect POL to GND. When driving an N-Channel MOSFET, connect POL to VL. These POL connections ensure the proper polarity for EXT. For design guidance in regard to this application, refer to the MAX1856 data sheet.

## \_Design Procedure Initial Specifications

In order to start the design procedure, a few parameters must be identified: the minimum input voltage expected (VIN(MIN)), the maximum input voltage expected (VIN(MAX)), the desired output voltage (VOUT), and the expected maximum load current (ILOAD).

#### Calculate the Equivalent Load Resistance

This is a simple calculation used to shorten the verification equations:

RLOAD = VOUT / ILOAD

Figure 1. Using an N-Channel MOSFET (MAX1847 only)

#### Calculate the Duty Cycle

The duty cycle is the ratio of the on-time of the MOSFET switch to the oscillator period. This is determined by the ratio of the input voltage to the output voltage. Since the input voltage typically has a range of operation, a minimum ( $D_{MIN}$ ) and maximum ( $D_{MAX}$ ) duty cycle is calculated by:

$$D_{MIN} = \frac{-V_{OUT} + V_{D}}{V_{IN(MAX)} - V_{SW} - V_{LIM} - V_{OUT} + V_{D}}$$

$$\mathsf{D}_{\mathsf{MAX}} \; = \; \frac{-\mathsf{V}_{\mathsf{OUT}} \; + \; \mathsf{V}_{\mathsf{D}}}{\mathsf{V}_{\mathsf{IN}(\mathsf{MIN})} - \mathsf{V}_{\mathsf{SW}} - \mathsf{V}_{\mathsf{LIM}} - \mathsf{V}_{\mathsf{OUT}} \; + \; \mathsf{V}_{\mathsf{D}}}$$

where VD is the forward drop across the output diode, Vsw is the drop across the external FET when on, and VLIM is the current-limit threshold. To begin with, assume VD = 0.5V for a Schottky diode, VsW = 100mV, and VLIM = 100mV. Remember that VOUT is negative when using this formula.

#### **Setting the Output Voltage**

The output voltage is set using two external resistors to form a resistive-divider to FB between the output and REF (refer to R1 and R2 in Figure 1). VREF is nominally

1.25V and the regulation voltage for FB is nominally 0. The load presented to the reference by the feedback resistors must be less than  $500\mu\text{A}$ . This is to guarantee that V<sub>REF</sub> is in regulation (see *Electrical Characteristics Table*). Conversely, the current through the feedback resistors must be large enough so that the leakage current of the FB input (50nA) is insignificant. Therefore, select R2 so that I<sub>R2</sub> is between  $50\mu\text{A}$  and  $250\mu\text{A}$ .

$$I_{R2} = V_{REF} / R2$$

where  $V_{REF}$  = 1.25V. A typical value for R2 is 10k $\Omega$ . Once R2 is selected, calculate R1 with the following equation:

$$R1 = R2 \times (-V_{OUT} / V_{REF})$$

#### **Setting the Operating Frequency**

The MAX1846/MAX1847 are capable of operating at switching frequencies from 100kHz to 500kHz. Choice of operating frequency depends on a number of factors:

Noise considerations may dictate setting (or synchronizing) fosc above or below a certain frequency or band of frequencies, particularly in RF applications.

- Higher frequencies allow the use of smaller value (hence smaller size) inductors and capacitors.

- Higher frequencies consume more operating power both to operate the IC and to charge and discharge the gate of the external FET. This tends to reduce the efficiency at light loads.

- 4) Higher frequencies may exhibit lower overall efficiency due to more transition losses in the FET; however, this shortcoming can often be nullified by trading some of the inductor and capacitor size benefits for lower-resistance components.

- 5) High-duty-cycle applications may require lower frequencies to accommodate the controller minimum off-time of 0.4µs. Calculate the maximum oscillator frequency with the following formula:

$$\begin{split} f_{OSC(MAX)} &= \frac{V_{IN(MIN)} - V_{SW} - V_{LIM}}{V_{IN(MIN)} - V_{SW} - V_{LIM} - V_{OUT} + V_{D}} \\ &\times \frac{1}{t_{OFF(MIN)}} \end{split}$$

Remember that VouT is negative when using this formula.

The oscillator frequency is set by a resistor, RFREQ, connected from FREQ to GND. The relationship between fosc (in Hz) and RFREQ (in  $\Omega$ ) is slightly nonlinear, as illustrated in the *Typical Operating Characteristics*. Choose the resistor value from the graph and check the oscillator frequency using the following formula:

$$f_{OSC} = \frac{1}{\left[\left(5.21 \times 10^{-7}\right) + \left(1.92 \times 10^{-11}\right) \times R_{FREQ} - \left(4.86 \times 10^{-19}\right) \times \left(R_{FREQ}\right)^{2}\right]}$$

#### External Synchronization (MAX1847 only)

The SYNC input provides external-clock synchronization (if desired). When SYNC is driven with an external clock, the frequency of the clock directly sets the MAX1847's switching frequency. A rising clock edge on SYNC is interpreted as a synchronization input. If the sync signal is lost, the internal oscillator takes over at the end of the last cycle, and the frequency is returned to the rate set by RFREQ. Choose RFREQ such that fosc = 0.9 x fsync.

#### **Choosing Inductance Value**

The inductance value determines the operation of the current-mode regulator. Except for low-current applica-

tions, most circuits are more efficient and economical operating in continuous mode, which refers to continuous current in the inductor. In continuous mode there is a trade-off between efficiency and transient response. Higher inductance means lower inductor ripple current, lower peak current, lower switching losses, and, therefore, higher efficiency. Lower inductance means higher inductor ripple current and faster transient response. A reasonable compromise is to choose the ratio of inductor ripple current to average continuous current at minimum duty cycle to be 0.4. Calculate the inductor ripple with the following formula:

I<sub>RIPPLE</sub> =

$$\frac{0.4 \times I_{LOAD(MAX)} \times \left(V_{IN(MAX)} - V_{SW} - V_{LIM} - V_{OUT} + V_{D}\right)}{\left(V_{IN(MAX)} - V_{SW} - V_{LIM}\right)}$$

Then calculate an inductance value:

Choose the closest standard value. Once again, remember that VOUT is negative when using this formula.

#### **Determining Peak Inductor Current**

The peak inductor current required for a particular output is:

$$ILPEAK = ILDC + (ILPP / 2)$$

where I<sub>LDC</sub> is the average DC input current and I<sub>LPP</sub> is the inductor peak-to-peak ripple current. The I<sub>LDC</sub> and I<sub>LPP</sub> terms are determined as follows:

$$\begin{split} I_{LDC} &= \frac{I_{LOAD} \times \left(-V_{OUT} + V_{D}\right)}{V_{IN(MIN)} - V_{SW} - V_{LIM}} \\ I_{LPP} &= \frac{\left(V_{IN(MIN)} - V_{SW} - V_{LIM}\right) \times \left(-V_{OUT} + V_{D}\right)}{L \times f_{OSC} \times \left(-V_{OUT} + V_{D}\right)} \end{split}$$

where L is the selected inductance value. The saturation rating of the selected inductor should meet or exceed the calculated value for I<sub>LPEAK</sub>, although most coil types can be operated up to 20% over their saturation rating without difficulty. In addition to the saturation criteria, the inductor should have as low a series resistance as possible. For continuous inductor current, the power loss in the inductor resistance (P<sub>LR</sub>) is approximated by:

where R<sub>L</sub> is the inductor series resistance.

Once the peak inductor current is calculated, the current sense resistor, Rcs, is determined by:

For high peak inductor currents (>1A), Kelvin-sensing connections should be used to connect CS and PGND to RCs. Connect PGND and GND together at the ground side of RCs. A lowpass filter between RCs and CS may be required to prevent switching noise from tripping the current-sense comparator at heavy loads. Connect a  $100\Omega$  resistor between CS and the high side of RCs, and connect a 1000pF capacitor between CS and GND.

#### **Checking Slope-Compensation Stability**

In a current-mode regulator, the cycle-by-cycle stability is dependent on slope compensation to prevent sub-harmonic oscillation at duty cycles greater than 50%. For the MAX1846/MAX1847, the internal slope compensation is optimized for a minimum inductor value (L<sub>MIN</sub>) with respect to duty cycle. For duty cycles greater then 50%, check stability by calculating LMIN using the following equation:

$$L_{MIN} = [(V_{IN(MIN)} \times R_{CS}) / M_{S}]$$

$$\times [(2 \times D_{MAX} - 1) / (1 - D_{MAX})]$$

where VIN(MIN) is the minimum expected input voltage,  $M_S$  is the Slope Compensation Ramp (41 mV/ $\mu$ s) and DMAX is the maximum expected duty cycle. If LMIN is larger than L, increase the value of L to the next standard value that is larger than LMIN to ensure slope compensation stability.

#### **Power MOSFET Selection**

The MAX1846/MAX1847 drive a wide variety of P-channel power MOSFETs (PFETs). The best performance, especially with input voltages below 5V, is achieved with low-threshold PFETs that specify on-resistance with a gate-to-source voltage (VGS) of 2.7V or less. When selecting a PFET, key parameters include:

- 1) Total gate charge (QG)

- 2) Reverse transfer capacitance (CRSS)

- 3) On-resistance (RDS(ON))

- 4) Maximum drain-to-source voltage (VDS(MAX))

- 5) Minimum threshold voltage (VTH(MIN))

At high switching rates, dynamic characteristics (parameters 1 and 2 above) that predict switching losses may have more impact on efficiency than RDS(ON), which predicts DC losses. QG includes all capacitance

associated with charging the gate. In addition, this parameter helps predict the current needed to drive the gate at the selected operating frequency. The power MOSFET in an inverting converter must have a high enough voltage rating to handle the input voltage plus the magnitude of the output voltage and any spikes induced by leakage inductance.

Choose RDS(ON)(MAX) specified at VGS < VIN(MIN) to be one to two times RCs. Verify that VIN(MAX) < VGS(MAX) and VDS(MAX) > VIN(MAX) - VOUT + VD. Choose the riseand fall-times (tR, tF) to be less than 50ns.

#### **Output Capacitor Selection**

The output capacitor (Cout) does all the filtering in an inverting converter. The output ripple is created by the variations in the charge stored in the output capacitor with each pulse and the voltage drop across the capacitor's equivalent series resistance (ESR) caused by the current into and out of the capacitor. There are two properties of the output capacitor that affect ripple voltage: the capacitance value, and the capacitor's ESR. The output ripple due to the output capacitor's value is given by:

$\label{eq:VRIPPLE-C} VRIPPLE-C = (I_{LOAD} \times D_{MAX} \times T_{OSC}) \ / \ Cout$  The output ripple due to the output capacitor's ESR is given by:

These two ripple voltages are additive and the total output ripple is:

The ESR-induced ripple usually dominates this last equation, so typically output capacitor selection is based mostly upon the capacitor's ESR, voltage rating, and ripple current rating. Use the following formula to determine the maximum ESR for a desired output ripple voltage (VRIPPLE-D):

Select a capacitor with ESR rating less than RESR. The value of this capacitor is highly dependent on dielectric type, package size, and voltage rating. In general, when choosing a capacitor, it is recommended to use low-ESR capacitor types such as ceramic, organic, or tantalum capacitors. Ensure that the selected capacitor has sufficient margin to safely handle the maximum ripple current (ILPP) and the maximum output voltage.

#### **Choosing Compensation Components**

The MAX1846/MAX1847 are externally loop-compensated devices. This provides flexibility in designs to accommodate a variety of applications. Proper com-

pensation of the control loop is important to prevent excessive output ripple and poor efficiency caused by instability. The goal of compensation is to cancel unwanted poles and zeros in the DC-DC converter's transfer function created by the power-switching and filter elements. More precisely, the objective of compensation is to ensure stability by ensuring that the DC-DC converter's phase shift is less than 180° by a safe margin, at the frequency where the loop gain falls below unity. One method for ensuring adequate phase margin is to introduce corresponding zeros and poles in the feedback network to approximate a single-pole response with a -20dB/decade slope all the way to unity-gain crossover.

#### Calculating Poles and Zeros

The MAX1846/MAX1847 current-mode architecture takes the double pole caused by the inductor and output capacitor and shifts one of these poles to a much higher frequency. This makes loop compensation easier. To compensate these devices, we must know the center frequencies of the right-half plane zero (z<sub>RHP</sub>) and the higher frequency pole (p<sub>OUT2</sub>). Calculate the z<sub>RHP</sub> frequency with the following formula:

$$ZRHP = \frac{-\left[\left(1 - D_{MAX}\right)^{2} \times \left(V_{IN(MIN)} - V_{OUT}\right) \times R_{LOAD}\right]}{\left(2\pi \times V_{OUT} \times L\right)}$$

The calculations for  $p_{OUT2}$  are very complex. For most applications where  $V_{OUT}$  does not exceed -48V (in a negative sense), the  $p_{OUT2}$  will not be lower than 1/8th of the oscillator frequency and is generally at a higher frequency than  $z_{RHP}$ . Therefore:

$$p_{OUT2} \ge 0.125 \times f_{OSC}$$

A pole is created by the output capacitor and the load resistance. This pole must also be compensated and its center frequency is given by the formula:

$$pout_1 = 1 / (2\pi \times RLOAD \times COUT)$$

Finally, there is a zero introduced by the ESR of the output capacitor. This zero is determined from the following equation:

$$z_{ESR} = 1 / (2\pi \times C_{OUT} \times R_{ESR})$$

#### Calculating the Required Pole Frequency

To ensure stability of the MAX1846/MAX1847, the introduced pole (PDOM) by the compensation network must roll-off the error amplifier gain to 1 before ZRHP or POUT2 occurs. First calculate the DC open-loop gain to determine the frequency of the pole to introduce.

$$A_{DC} = \frac{\begin{bmatrix} G_{M} \times R_{O} \times (1 - D_{MAX})^{2} \times (V_{IN(MIN)} - V_{OUT}) \\ \times R_{LOAD} \end{bmatrix}}{B \times \begin{bmatrix} (R_{CS} \times V_{IN(MIN)}) + T_{OSC}(1 - D_{MAX}) \\ \times R_{LOAD} (\frac{V_{IN(MIN)}}{2L} \times R_{CS} + M_{S1}) \end{bmatrix}}$$

where:

B is the feedback divider attenuation factor = (-Vout / VREF),

$G_M$  is the error amplifier transconductance =  $400 \,\mu\text{A/V}$ ,

Ro is the error amplifier output resistance =  $3 \text{ M}\Omega$ ,

$M_{S1}$  is the slope compensation factor =  $[(1.636A/\mu s) \times R_{CS}]$ ,

RCS is the selected current sense resistor,

L is the selected inductance value

If ZRHP is at a lower frequency than pout2, the required dominant pole frequency is given by:

Otherwise the required dominant pole frequency is:

### Determining the Compensation Component Values

Using pDOM, calculate the compensation capacitor required:

$$C_{COMP} = 1 / (2\pi \times R_{O} \times p_{DOM})$$

Select the next largest standard value of capacitor and then calculate the compensation resistor required to cancel out the output-capacitor-induced pole (pout1) determined previously. A zero is needed to cancel the output-induced pole and the frequency of this zero must equal pout1. Therefore:

$$ZCOMP = POUT1$$

$RCOMP = RLOAD \times COUT / CCOMP$

Choose the nearest lower standard value of the resistor. Now check the final values selected for the compensation components:

$$PCOMP = 1 / [2\pi \times CCOMP \times (RO + RCOMP)]$$

In order for pcomp to compensate the loop, the openloop gain must reach unity at a lower frequency than the right-half-plane zero or the second output pole, whichever is lower in frequency. If the second output pole and the right-half-plane zero are close together in frequency, the higher resulting phase shift at unity gain

may require a larger compensation capacitor than calculated. It might take more than a couple of iterations to obtain a suitable combination.

Finally, the zero introduced by the output capacitor's ESR must be compensated. This is accomplished by placing a capacitor between REF and FB creating a pole directly in the feedback loop. Calculate the value of this capacitor using the frequency of zesp and the selected feedback resistor values with the formula:

$$C_{FB} = R_{ESR} \times C_{OUT} \times \frac{R_1 + R_2}{R_1 \times R_2}$$

## Applications Information Maximum Output Power

The maximum output power that the MAX1846/MAX1847 can provide depends on the maximum input power available and the circuit's efficiency:

$$POUT(MAX) = Efficiency \times PIN(MAX)$$

Furthermore, the efficiency and input power are both functions of component selection. Efficiency losses can be divided into three categories: 1) resistive losses across the inductor, MOSFET on-resistance, current-sense resistor, and the ESR of the input and output capacitors; 2) switching losses due to the MOSFET's transition region, and charging the MOSFET's gate capacitance; and 3) inductor core losses. Typically 80% efficiency can be assumed for initial calculations. The required input power depends on the inductor current limit, input voltage, output voltage, output current, inductor value, and the switching frequency. The maximum output power is approximated by the following formula:

where ILIM is the peak current limit and LIR is the inductor current-ripple ratio and is calculated by:

Again, remember that V<sub>OUT</sub> for the MAX1846/MAX1847 is negative.

#### **Diode Selection**

The MAX1846/MAX1847's high-switching frequency demands a high-speed rectifier. Schottky diodes are recommended for most applications because of their fast recovery time and low forward voltage. Ensure that the diode's average current rating exceeds the peak inductor current by using the diode manufacturer's data. Additionally, the diode's reverse breakdown voltage must

exceed the potential difference between VouT and the input voltage plus the leakage inductance spikes. For high output voltages (-50V or more), Schottky diodes may not be practical because of this voltage requirement. In these cases, use an ultrafast recovery diode with adequate reverse-breakdown voltage.

#### **Input Filter Capacitor**

The input capacitor (C<sub>IN</sub>) in inverting converter designs reduces the current peaks drawn from the input supply and reduces noise injection. The source impedance of the input supply largely determines the value of C<sub>IN</sub>. High source impedance requires high input capacitance, particularly as the input voltage falls. Since inverting converters act as "constant-power" loads to their input supply, input current rises as the input voltage falls. Consequently, in low-input-voltage designs, increasing C<sub>IN</sub> and/or lowering its ESR can add as much as 5% to the conversion efficiency.

#### **Bypass Capacitor**

In addition to C<sub>IN</sub> and C<sub>OUT</sub>, other ceramic bypass capacitors are required with the MAX1846/MAX1847. Bypass REF to GND with a 0.1 $\mu$ F or larger capacitor. Bypass V<sub>L</sub> to GND with a 0.47 $\mu$ F or larger capacitor. All bypass capacitors should be located as close to their respective pins as possible.

#### **PC Board Layout Guidelines**

Good PC board layout and routing are required in high-frequency-switching power supplies to achieve good regulation, high efficiency, and stability. It is strongly recommended that the evaluation kit PC board layouts be followed as closely as possible. Place power components as close together as possible, keeping their traces short, direct, and wide. Avoid interconnecting the ground pins of the power components using vias through an internal ground plane. Instead, keep the power components close together and route them in a "star" ground configuration using component-side copper, then connect the star ground to internal ground using multiple vias.

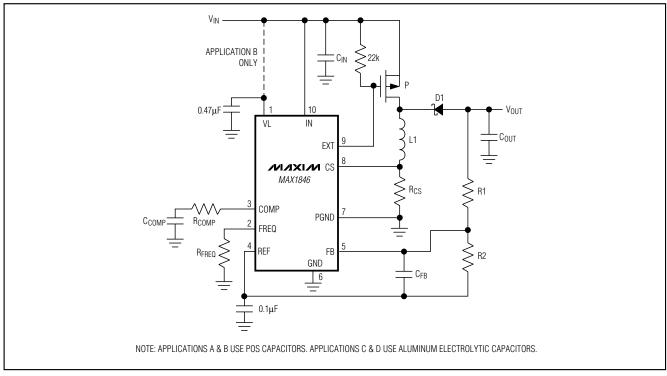

### Main Application Circuits

The MAX1846/MAX1847 are extremely versatile devices. Figure 2 shows a generic schematic of the MAX1846. Table 1 lists component values for several typical applications. These component values also apply to the MAX1847. The first two applications are featured in the MAX1846/MAX1847 EV Kit.

Figure 2. MAX1846 Main Application Circuit

**Table 1. Component List for Main Application Circuits**

| CIRCUIT ID                  | Α        | В        | С        | D        |

|-----------------------------|----------|----------|----------|----------|

| Input (V)                   | 12       | 3 to 5.5 | 12       | 12       |

| Output (V)                  | -5       | -12      | -48      | -72      |

| Output (A)                  | 2        | 0.4      | 0.1      | 0.1      |

| C <sub>COMP</sub> (µF)      | 0.047    | 0.22     | 0.068    | 0.1      |

| C <sub>IN</sub> (µF)        | 3 x 10   | 3 x 22   | 10       | 10       |

| C <sub>OUT</sub> (µF)       | 2 x 100  | 2 x 47   | 47       | 33       |

| C <sub>FB</sub> (pF)        | 390      | 1200     | 1800     | 1800     |

| R1 (kΩ) (1%)                | 40.2     | 95.3     | 383      | 576      |

| R2 (kΩ) (1%)                | 10       | 10       | 10       | 10       |

| R <sub>COMP</sub> (kΩ)      | 8.2      | 10       | 150      | 1800     |

| $R_{CS}\left(\Omega\right)$ | 0.02     | 0.02     | 0.05     | 0.05     |

| R <sub>FREQ</sub> (kΩ)      | 150      | 150      | 150      | 150      |

| D1                          | CMSH5-40 | CMSH5-40 | CMR1U-02 | CMR1U-02 |

| L1 (µH)                     | 10       | 10       | 47       | 82       |

| P1                          | FDS6685  | FDS6375  | IRFR5410 | IRFR5410 |

### **Component Suppliers**

| SUPPLIER                   | COMPONENT             | PHONE        | WEBSITE                                  |  |

|----------------------------|-----------------------|--------------|------------------------------------------|--|

| AVX                        | Capacitors            | 803-946-0690 | www.avxcorp.com                          |  |

| Central Semiconductor      | Diodes                | 516-435-1110 | www.centralsemi.com                      |  |

| Coilcraft                  | Inductors             | 847-639-6400 | www.coilcraft.com                        |  |

| Dale                       | Resistors             | 402-564-3131 | www.vishay.com/brands/dale/main.html     |  |

| Fairchild                  | MOSFETs               | 408-721-2181 | www.fairchildsemi.com                    |  |

| International<br>Rectifier | MOSFETs               | 310-322-3331 | www.irf.com                              |  |

| IRC                        | Resistors             | 512-992-7900 | www.irctt.com                            |  |

| Kemet                      | Capacitors            | 864-963-6300 | www.kemet.com                            |  |

| On Semiconductor           | MOSFETs, Diodes       | 602-303-5454 | www.onsemi.com                           |  |

| Panasonic                  | Capacitors, Resistors | 201-348-7522 | www.panasonic.com                        |  |

| Sanyo                      | Capacitors            | 619-661-6835 | www.secc.co.jp                           |  |

| Siliconix                  | MOSFETs               | 408-988-8000 | www.siliconix.com                        |  |

| Sprague                    | Capacitors            | 603-224-1961 | www.vishay.com/brands/sprague/main.html  |  |

| Sumida                     | Inductors             | 847-956-0666 | www.remtechcorp.com                      |  |

| Vitramon                   | Resistors             | 203-268-6261 | www.vishay.com/brands/vitramon/main.html |  |

Note: Please indicate that you are using the MAX1846/MAX1847 when contacting these component suppliers.

## **Pin Configurations**

## \_Chip Information

TRANSISTOR COUNT: 2441

PROCESS TECHNOLOGY: BICMOS

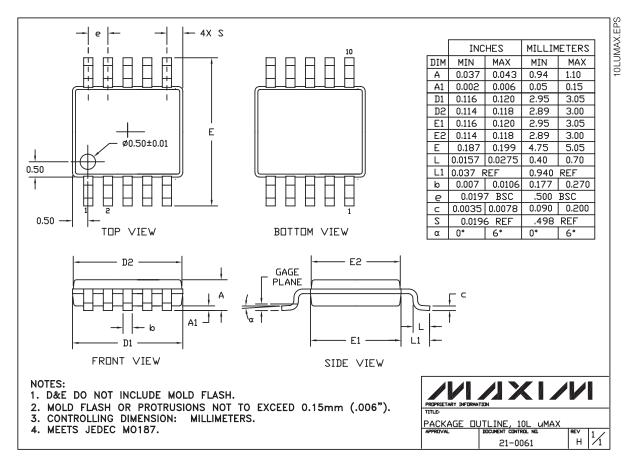

## Package Information

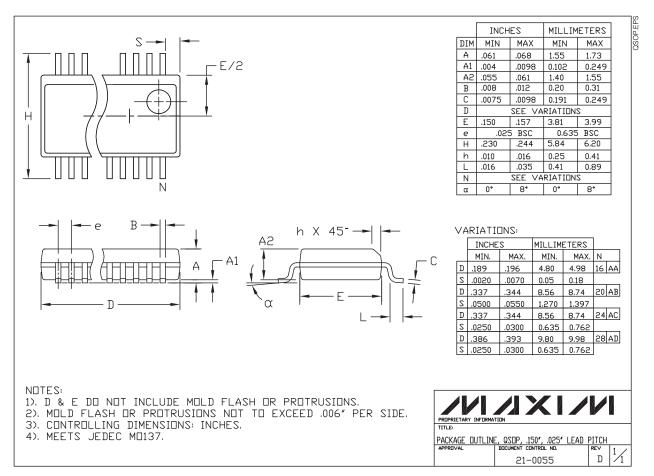

## Package Information (continued)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.